3D芯片堆疊技術(shù)到底是什么?

現(xiàn)在3D芯片堆疊技術(shù)具有如此巨大的魅力,它集成了存儲(chǔ),邏輯和傳感器,可以減小尺寸并提供性能,這可以說(shuō)是邁向摩爾定律的一步。所以3D芯片堆疊技術(shù)到底是什么?

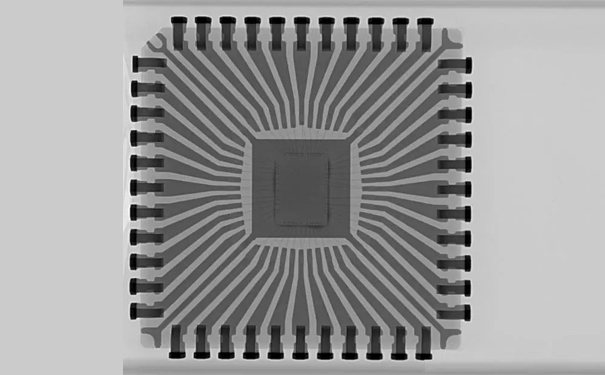

與將所有模塊都放在平面層上的傳統(tǒng)二維芯片相比,該三維芯片允許多層堆疊,而TSV用于提供多個(gè)晶圓的垂直通信。其中,TSV是3D芯片堆疊技術(shù)的關(guān)鍵。

3D堆疊技術(shù)是利用堆疊技術(shù)或通過(guò)互連和其他微加工技術(shù)在芯片或結(jié)構(gòu)的Z軸方向上形成三維集成,信號(hào)連接以及晶圓級(jí),芯片級(jí)和硅蓋封裝具有不同的功能。針對(duì)包裝和可靠性技術(shù)的三維堆疊處理技術(shù),該技術(shù)用于微系統(tǒng)集成,是在片上系統(tǒng)(SOC)和多芯片模塊(MCM)之后開(kāi)發(fā)的先進(jìn)的系統(tǒng)級(jí)封裝制造技術(shù)。

在傳統(tǒng)的SiP封裝系統(tǒng)中,任何芯片堆棧都可以稱(chēng)為3D,因?yàn)樵赯軸上功能和信號(hào)都有擴(kuò)展,無(wú)論堆棧位于IC內(nèi)部還是外部。目前,3D芯片技術(shù)的類(lèi)別如下:

1.基于芯片堆疊的3D技術(shù)

3D IC的初始形式仍廣泛用于SiP領(lǐng)域。具有相同功能的裸芯片從下到上堆疊以形成3D堆疊,然后通過(guò)兩側(cè)的接合線進(jìn)行連接,**以系統(tǒng)級(jí)封裝(System-in-Package,SiP)的形式連接。堆疊方法可以是金字塔形,懸臂式,并排堆疊和其他方法。

另一種常見(jiàn)的方法是在SiP基板上安裝倒裝芯片裸芯片,并通過(guò)粘接將另一個(gè)裸芯片安裝在其頂部,如下圖所示,這種3D解決方案在手機(jī)中更為常用。

2.基于有源TSV的3D技術(shù)

在這種3D集成技術(shù)中,至少一個(gè)裸芯片與另一個(gè)裸芯片堆疊在一起。下部裸芯片使用TSV技術(shù),上部裸芯片通過(guò)TSV與下部裸芯片和SiP基板通信 。

以上技術(shù)涉及在芯片處理完成之后堆疊以形成3D。實(shí)際上,它不能被稱(chēng)為真正的3D IC技術(shù)。這些方法基本上是在封裝階段進(jìn)行的,我們可以稱(chēng)其為3D集成,3D封裝或3D SiP技術(shù)。

3.基于無(wú)源TSV的3D技術(shù)

中介層硅襯底放置在SiP襯底和裸芯片之間。中介層具有硅通孔(TSV),并且硅襯底上表面和下表面上的金屬層通過(guò)TSV連接。有人將此技術(shù)稱(chēng)為2.5D,因?yàn)樽鳛橹薪閷拥墓杌迨菬o(wú)源組件,并且TSV硅過(guò)孔未在芯片本身上打孔。

4.基于芯片制造的3D技術(shù)當(dāng)前,基于芯片制造的3D技術(shù)主要應(yīng)用于3D NAND FLASH。東芝和三星在3D NAND方面的開(kāi)拓性工作帶來(lái)了兩項(xiàng)主要的3D NAND技術(shù)。 3D NAND現(xiàn)在可以達(dá)到64層甚至更高的層,其輸出已經(jīng)超過(guò)2D NAND。

芯片技術(shù)不斷發(fā)展,這也考驗(yàn)了相應(yīng)的芯片封裝測(cè)試技術(shù),日聯(lián)科技不斷探索X射線成像檢測(cè)技術(shù),力求在芯片發(fā)展的道路上貢獻(xiàn)自己的 一臂之力。

了解更多日聯(lián)科技X-ray檢測(cè)裝備信息可以撥打全國(guó)服務(wù)熱線:400-880-1456 或訪問(wèn)日聯(lián)科技官網(wǎng):www.0t23t.com